Skematik Pemodelan Titin

TAHAPAN PEMBUATAN MODEL DALAM PEMODELAN

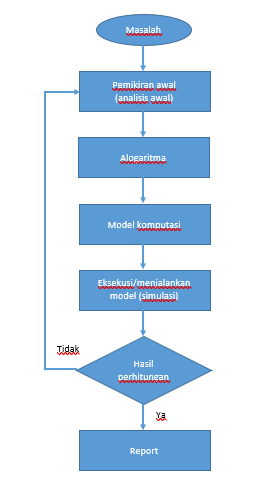

Adapun susunan proses dalam pemodelan adalah sebagai berikut:

Langkah-langkah Pembuatan Model Simulasi

Untuk pembuatan model simulasi model yang dibangun harus kredibel. Representasi kredibel sistem nyata oleh model simulasi ditunjukkan oleh verifikasi dan validasi model. Verifikasi adalah proses pemeriksaan apakah logika operasional model (program komputer) sesuai dengan logika diagram alur. Kalimat sederhananya, apakah ada kesalahan dalam program? (Hoover dan Perry, 1989); verifikasi adalah pemeriksaan apakah program komputer simulasi berjalan sesuai dengan yang diinginkan, dengan pemeriksaan program komputer. Verifikasi memeriksa penerjemahan model simulasi konseptual (diagram alur dan asumsi) ke dalam bahasa pemrograman secara benar (Law dan Kelton, 1991) .

Validasi adalah proses penentuan apakah model, sebagai konseptualisasi atau abstraksi, merupakan representasi berarti dan akurat dari sistem nyata? (Hoover dan Perry, 1989); validasi adalah penentuan apakah model konseptual simulasi (sebagai tandingan program komputer) adalah representasi akurat dari sistem nyata yang sedang dimodelkan (Law dan Kelton, 1991).

Aturan Verifikasi Dan Validasi Dalam Simulasi

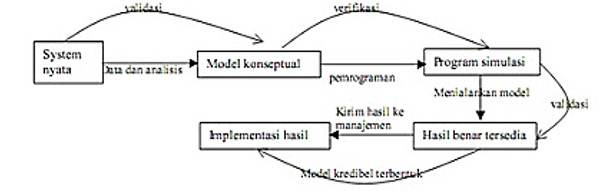

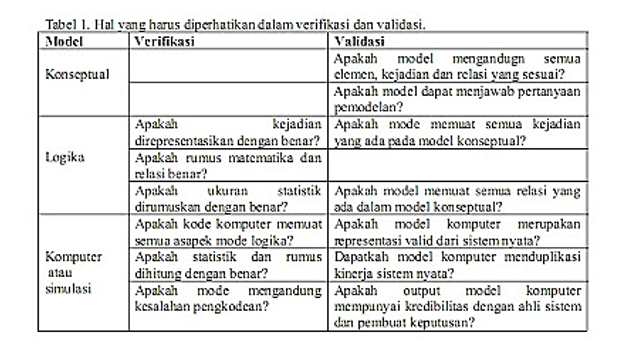

Ketika membangun model simulasi sistem nyata, kita harus melewati beberapa tahapan atau level pemodelan. Seperti yang dapat dilihat pada Gambar 1, pertama kita harus membangun model konseptual yang memuat elemen sistem nyata. Dari model konseptual ini kita membangun model logika yang memuat relasi logis antara elemen sistem juga variabel eksogenus yang mempengaruhi sistem. Model kedua ini sering disebut sebagai model diagram alur. Menggunakan model diagram alur ini, lalu dikembangkan program komputer, yang disebut juga sebagai model simulasi, yang akan mengeksekusi model diagram alur.

Pengembangan model simulasi merupakan proses iteratif dengan beberapa perubahan kecil pada setiap tahap. Dasar iterasi antara model yang berbeda adalah kesuksesan atau kegagalan ketika verifikasi dan validasi setiap model. Ketika validasi model dilakukan, kita mengembangkan representasi kredibel sistem nyata, ketika verifikasi dilakukan kita memeriksa apakah logika model diimplementasikan dengan benar atau tidak. Karena verifikasi dan validasi berbeda, teknik yang digunakan untuk yang satu tidak selalu bermanfaat untuk yang lain Baik untuk verifikasi atau validasi model, kita harus membangun sekumpulan kriteria untuk menilai apakah diagram alur model dan logika internal adalah benar dan apakah model konseptual representasi valid dari sistem nyata. Bersamaan dengan kriteria evaluasi model, kita harus spesifikasikan siapa yang akan mengaplikasikan kriteria dan menilai seberapa dekat kriteria itu memenuhi apa yang sebenarnya.

Verifikasi dan Validasi Model Logis

Bentuk model logis tergantung dari bahasa pemrograman yang akan digunakan. Jika model konseptual sudah dibangun dengan baik, verifikasi model konseptual bukan pekerjaan kompleks. Ada beberapa pertanyaan yang harus dijawab sebelum kita yakin bahwa model logis merepresentasikan model konseptual. Salah satu pendekatan yang digunakan untuk verifikasi model logis adalah dengan fokus pada:

1. apakah kejadian dalam model diproses dengan benar?

2. apakah rumus matematika dan relasi dalam model valid?

3. apakah statistik dan ukuran kinerja diukur dengan benar?